# MK2698A Wide-VCC Range, Multi-Mode HF QR Controller

## 1. Description

MK2698A is a highly integrated multiple-mode QR controller for high performance, low standby current and cost-effective offline flyback converter applications.

In order to achieve high efficiency from universal line with wide output voltage range across different load, MK2698A is self-adaptive to operate at DCM/QR modes accordingly with valley switching as much as possible.

MK2698A offers comprehensive protection features including output over-voltage protection (OVP), output over power protection (OPP), VCC over-voltage protection, Brown-in/out, and output short protection, Pin open/short protection.

MK2698A is available in SOT23-6 package.

# 2. Typical Applications

- AC/DC Adapter

- AC/DC general power supply

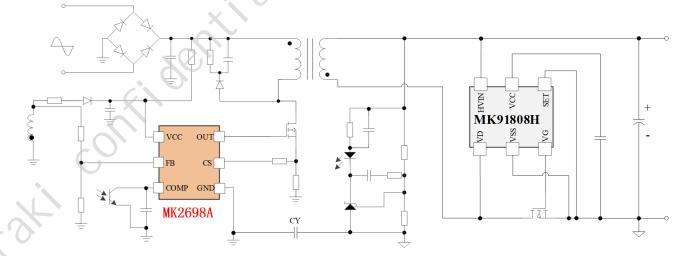

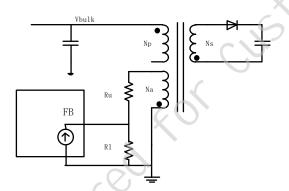

# 4. Simplified Application

## 3. Features

- Wide VCC Operating Range (10V to 88V)

- Working Frequency up to 130k Hz

- Adaptive Multi-Mode Control Optimized for Different Output Voltages and Load Currents

- Proprietary Soft-start Scheme to Achieve Low SR Vds Stress

- Optimized High Efficiency at Light Load

- OPP/SSCP Protection

- Brown-in /Brown-out Function

- VCC OVP /VO OVP Protection

- PIN open/short Protection

- External Programmable OTP Protection

- Support Wide Output Voltage Ranges

- Frequency Dithering to Improve EMI Performance

- Tiny SOT23-6 Package

# 5. Ordering Information

| Ordering No. | Description                 |  |

|--------------|-----------------------------|--|

| MK2698AGSA   | SOT23-6, 3000pcs/reel, MSL1 |  |

# 6. Package Reference

## Absolute maximum Ratings (1)

| VCC                            | -0.3V to +100V  |

|--------------------------------|-----------------|

| COMP, FB                       | 0.3V to +5.5V   |

| CS                             |                 |

| OUT                            |                 |

| Operating Junction Temperature | -40°C to +150°C |

| Recommended Operation Conditions               |                                             |  |  |  |  |

|------------------------------------------------|---------------------------------------------|--|--|--|--|

| VCC10V to 88V                                  |                                             |  |  |  |  |

| Maximum Junction Temp. (T <sub>J</sub> )+125°C |                                             |  |  |  |  |

| Thermal Resistance                             | $oldsymbol{	heta}$ JA $oldsymbol{	heta}$ JC |  |  |  |  |

SOT23-6......110 74 °C/W

#### Notes:

(1) Exceeding these ratings may damage the device.

# 7. Electrical Characteristics

## T<sub>A</sub>=25°C, unless otherwise noted.

| Parameter                                                          | Symbol                | Conditions                             | Min  | Тур   | Max  | Units  |

|--------------------------------------------------------------------|-----------------------|----------------------------------------|------|-------|------|--------|

| Supply Management Se                                               | ection                |                                        |      |       |      |        |

| VCC UVLO Rising                                                    | V <sub>CC_ON</sub>    |                                        | 14.5 | 17    | 19.5 | V      |

| VCC UVLO Falling                                                   | Vcc_off               |                                        | 6    | 7.2   | 8.5  | V      |

| VCC UVLO Hysteresis                                                | Vcc_hyst              |                                        |      | 10    |      | V      |

| VCC Startup current                                                | ISTARTUP              |                                        | 2    | 5     | 10   | uA     |

| VCC Normal Operating Current                                       | Гор                   | COMP=2V, GATE=1nF to<br>GND; Fsw=65kHz | 1.4  | 2.5   | 3    | mA     |

| Burst Operating Current                                            | IBURST                | COMP=0V, GATE=1nF to GND               | 200  | 280   | 400  | uA     |

| VCC Hold Threshold                                                 | V <sub>CC_HOLD</sub>  |                                        | 7    | 8.3   | 9.6  | V      |

| VCC OVP Threshold                                                  | Vcc_ovp               |                                        | 89   | 93    | 100  | V      |

| VCC CLAMP Threshold                                                | V <sub>CC_CLAMP</sub> |                                        | 10.  | 102   |      | V      |

| Comp Input Section                                                 | _                     | .0                                     | }    |       |      |        |

| COMP Open Voltage                                                  | V <sub>COMP_OP</sub>  | COMP pin open-circuited                |      | 4.4   |      | V      |

| COMP Short-Circuit Current                                         | ICOMP_SHORT           | COMP=0V                                | 100  | 150   | 250  | uA     |

| Burst Mode Entry<br>Voltage                                        | V <sub>ВМ_ЕТ</sub>    |                                        | 0.25 | 0.3   | 0.35 | V      |

| Burst Mode Hysteresis                                              |                       | 0                                      |      | 0.05  |      | V      |

| OPP Protection Threshold                                           | VOPP                  |                                        | 2.7  | 3     | 3.3  | V      |

| OPP Deglitch Time*                                                 | T <sub>D_OPP</sub>    |                                        |      | TSS*6 |      | ms     |

| COMP to CS Gain                                                    | Avcs                  |                                        | 2.4  | 2.5   | 2.6  | V/V    |

| Current Sense Input (C                                             | S PIN) Section        |                                        |      |       |      |        |

| Soft Start Time of CS<br>Threshold                                 | Tss                   |                                        | 4    | 7     | 10   | ms     |

| Leading Edge Blanking Time                                         | T <sub>LEB</sub>      |                                        | 200  | 330   | 500  | ns     |

| Secondary Rectifier<br>short circuit trigger<br>voltage (OC FAULT) | Vsr_sh                |                                        | 1.1  | 1.2   | 1.3  | V      |

| SR Short circuit deglitch cycles*                                  |                       |                                        |      | 3     |      | Cycles |

| Cycle by Cycle Current<br>Limit                                    | V <sub>CS_CBC</sub>   | VFB<1V, IFB=100uA                      | 0.8  | 0.85  | 0.9  | V      |

|                                                | 1                    | T                  | 1     | Т     | 1    | _            |

|------------------------------------------------|----------------------|--------------------|-------|-------|------|--------------|

| Cycle by Cycle Current<br>Limit                | Vcs_cbc              | VFB<1V, IFB=300uA  | 0.56  | 0.65  | 0.7  | V            |

| Comp and Control Delay                         | T <sub>DL_</sub> cs  |                    |       | 130   | 200  | ns           |

| FB Input Section                               |                      |                    |       |       |      |              |

| Brown-in Detection                             |                      |                    |       |       |      |              |

| Threshold                                      | I <sub>BNI</sub>     |                    | 82    | 94    | 99   | uA           |

| Brown-out Detection Threshold                  | I <sub>BNO</sub>     |                    | 74    | 85    | 93   | uA           |

|                                                |                      |                    |       |       |      | <del>)</del> |

| Brown-out Deglitch Time*                       | T <sub>BL_BNO</sub>  |                    |       | Tss*7 |      | ms           |

| FB OVP Threshold                               | V <sub>FB_OVP</sub>  |                    | 3.3   | 3.6   | 3.9  | ٧            |

| FB OVP Deglitch Time*                          | T <sub>BL_OVP</sub>  |                    |       | 7     | J    | cycles       |

| FB UVP Threshold (Output Short)                | V <sub>FB_ST</sub>   |                    | 0.25  | 0.3   | 0.35 | V            |

| FB UVP Threshold (Output Short) Deglitch Time* | T <sub>BL_</sub> ST  |                    | S. S. | 7     |      | cycles       |

| FB Sampling Time                               | T <sub>SAMPL</sub>   | CS=0.5V            | 1     | 1.4   | 1.8  | us           |

| Valley Detection Threshold                     | IFB_VALLEY           | 01                 |       | 10    |      | uA           |

| FB High Threshold                              | V <sub>FB_H</sub>    |                    | 1.7   | 1.9   | 2.1  | V            |

| FB Middle Threshold                            | V <sub>FB_M</sub>    |                    | 0.9   | 1     | 1.2  | V            |

| Gate Drive (OUT PIN) Se                        | ection               |                    |       |       |      |              |

| GATE Low Level                                 | V <sub>G_L</sub>     |                    |       | 0.2   | 0.5  | V            |

| GATE High Level                                | V <sub>G_H</sub>     | VCC=13V, Load=20mA | 8     | 9.5   | 10.5 | V            |

| GATE Clamp Voltage                             | V <sub>G_HC</sub>    |                    |       | 12    | 12.5 | V            |

| GATE Rising Time                               | Tr                   | Cload=1nF          | 300   | 400   | 500  | ns           |

| GATE Falling Time                              | Tf                   | Cload=1nF          | 10    | 30    | 50   | ns           |

| Control Law                                    | 2)                   |                    |       |       |      |              |

| Normal Mode<br>Frequency                       | Fsw_max              |                    | 117   | 130   | 143  | kHz          |

| Green Mode Frequency                           | Fsw_green            |                    | 21    | 25    | 29   | kHz          |

| Dithering Range*                               |                      |                    |       | ±6    |      | %            |

| Dithering Period*                              |                      |                    |       | 8     |      | ms           |

| Maximum Toff Time                              | Toff_MAX             |                    | 80    | 105   | 200  | us           |

| Thermal Shutdown Threshold*                    | Th <sub>SD</sub>     |                    |       | 155   |      | $^{\circ}$   |

| Thermal Shutdown Hysteresis*                   | Th <sub>SD_hys</sub> |                    |       | 30    |      | $^{\circ}$   |

## Note

\* Guaranteed by design

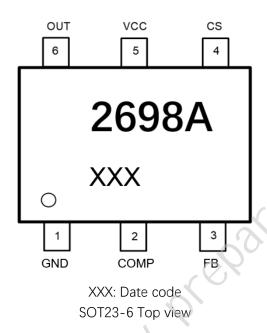

# 8. Pin Functions

| Pin# | Name | Description             |   |

|------|------|-------------------------|---|

| 1    | GND  | Ground                  |   |

| 2    | COMP | Voltage feedback pin    |   |

| 3    | FB   | Auxiliary voltage sense |   |

| 4    | CS   | Current sense input     |   |

| 5    | VCC  | Power supply            |   |

| 6    | OUT  | Output to drive MOSFET  | C |

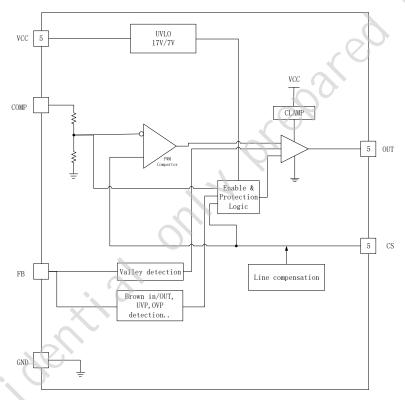

# 9. Block Diagram

Figure 1. Functional Block Diagram

## 10. Operation Descriptions

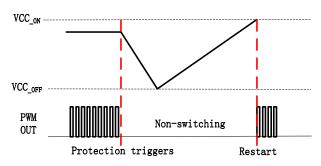

## Vcc and Start-up

MK2698A's start-up current is only  $\sim$ 5 uA so that a large value of start-up resistor can be used to charge up VCC while minimize power loss during start-up. Once VCC reaches above UVLO threshold  $V_{\text{CC\_ON}}$ , MK2698A starts switching.

#### **Soft Start**

MK2698A features an internal ~7ms soft-start to reduce electrical stress in power system during start-up. In order to reduce the voltage stresses from high peak current and high frequency switching further, MK2698A operates at optimized frequencies and control modes accordingly to output voltages and synchronous rectifier controller start-up status.

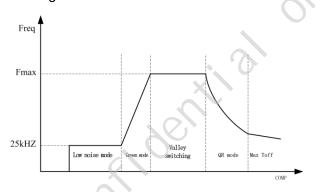

## **Operation Curve**

MK2698A works on different modes which are based on COMP voltage and output voltage. In order to achieve optimal efficiency at certain output voltage range, MK2698A detects FB voltage to determine the switching frequency and working mode.

#### Brown in/ Brown out

When the power MOSFET is turned on, the voltage at auxiliary windings is negative which makes Brown-in/Brown-out protection feasible. When system starts up, power MOSFET is on, the current flow out of FB pin is equal to:

$$\frac{V_{BULK}*Na}{Ru*Np}$$

If this current is larger than I<sub>BNI</sub> for four switching cycles, the controller starts to soft-start; otherwise,

Brown-in auto-recovery protection is triggered. During normal operation, when power MOSFET is turned on, the current at FB is less than  $I_{BN0}$  for at least  $T_{BL\_BNO}$  (~49ms), the controller enters Brown-out auto-recovery protection.

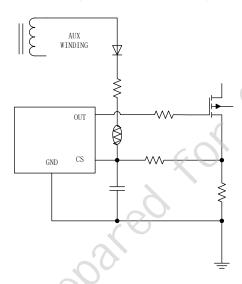

#### **Current Sense (OPP)**

MK2698A is current mode PWM controller. Cycle-by-cycle current limiting is offered. The switch current is detected by a sense resistor at CS pin. An internal leading-edge blanking circuit with T<sub>LEB</sub> blanking time blocks the sensed voltage spikes at initial power MOSFET on state due to snubber diode reverse recovery and surge gate current at power MOSFET. The maximum cycle-by-cycle current limit is set by V<sub>CS\_CBC</sub>/R<sub>CS</sub>.

#### **Line Compensation**

MK2698A uses the detected input line voltage through the current at FB pin (I<sub>FB</sub>) to generate the offset voltage added on internal current signal to compensate the output OPP power level. This mechanism helps achieve flat OPP power level over different input voltage.

#### Voltage Feedback Loop

COMP is the voltage loop feedback pin which is connected to TL431 output through opto-coupler. In order to support wide COMP range, a ratio of 1/2.5 resistor divider is used before it goes to PWM comparator.

A ceramic capacitor is suggested to put parallel with the resistor which is series with optocoupler diode.

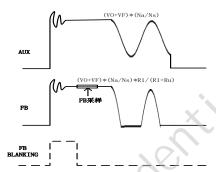

## **FB Voltage Detection**

MK2698A detects the transformer core demagnetization by monitoring the signal at the auxiliary windings through FB pin.

By detecting FB voltage during demagnetization time, MK2698A is able to do the following functions:

Output over voltage protection (OVP): FB is above  $V_{FB\_OVP}$  (~3.6V) for 7 switching cycles Output under voltage protection (output short circuit protection): FB is below  $V_{FB\_ST}$  (~0.2V) for 7 switching cycles

Determine control mode and switching frequency based on  $V_{FB\ H},\,V_{FB\ M_{\odot}}$

MK2698A implements a FB blanking time to block the switching noise at the beginning of the transformer demagnetizing time. The FB blanking time is proportional to Vcs since the switching noise is generally bigger with larger peak current.

## Valley Switching

After secondary side rectification is done, the drain voltage starts oscillating with a frequency of approximately

$$1/2 \pi \sqrt{Coss * L_P}$$

,

where Lp is the inductance of primary winding of the transformer and COSS is capacitance on the drain of primary MOSFET. When the oscillation ringing is below 0 at auxiliary winding, MK2698A clamps FB pin to ~0V, and senses the current at FB pin. When the current out of FB reaches a design value, a "possible" valley is locked and MK2698A turns on after propagation delay. If DCM ringing is dampened very quickly so that a valley is not able to be determined, MK2698A is going to turn on after 3us from falling edge of internal oscillator clock.

#### **Protection**

Reliable power supply system is achieved with auto-recovery protections including cycle-by-cycle current limit, over-power-protection (OPP), output over-voltage protection, etc. Detailed protection features are described in the following sessions.

If the protection is restart mode, the IC will actively pull VCC down to VCC OFF before restarting, with a maximum pull-down current of about 220uA. If the startup resistor is set too small, causing the startup current to be greater than the IC's pull-down current, VCC cannot be pulled down to VCC\_OFF, and MK2698A will not be able to complete the restart action.

| MK2698A Protection | MK2698A Protection |

|--------------------|--------------------|

| Features           | Schemes            |

| OPP                | Restart            |

| VO_OVP             | Restart            |

| VCC_OVP            | Restart            |

| CS_SHORT           | Restart            |

| SSCP               | Restart            |

| FB_UVP (VO_SCP)    | Restart            |

#### **Over Power Protection**

OPP is achieved by monitoring COMP voltage. If COMP voltage is above  $V_{\text{OPP}}$  for at least 7 times of soft-start time, MK2698A enters auto-recovery OPP protection.

# Secondary Short Circuit Protection (SSCP)

If secondary side synchronous rectifier is short circuit, peak current increases rapidly after power MOSFET is turned on, thus the protection needs to react in much less wait time. MK2698A shortens current sense blanking time to  $T_{LEB\_SRSH}$  if CS pin detects a voltage above  $V_{SR\_SH}$  (~1.2V) threshold, and turns off power MOSFET immediately for current switching cycle. If this happens for consecutive three switching cycles, controller goes to auto-recovery SSCP protection.

#### Vcc OVP

Whenever the VCC voltage is higher than the OVP threshold voltage VCC\_OVP, the output gate drive circuit will be shutdown simultaneously to stop the switching of the power MOSFET and goes to auto-recovery protection.

#### **OTP**

There is OTP protection inside MK2698A with Thsd triggering temperature.

MK2698A is implemented over temperature

protection outside on CS pin which senses voltage to monitor NTC status during MOSFET off region. If VCS is greater than V<sub>CS\_CBC</sub> and continues for 15 cycles, OTP is triggered, MK2698A goes to auto-recovery OTP protection.

## **Pin Open Short Protection**

There are several critical protections designed in the MK2698A to prevent the power supply at fault state. In case listed below, MK2698A will trigger protection:

- Adjacent PINS short

- PINS open

- CS short

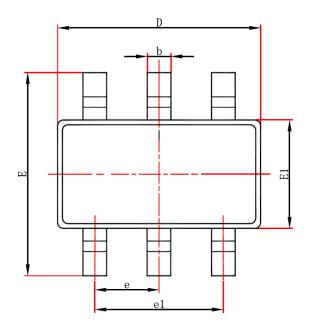

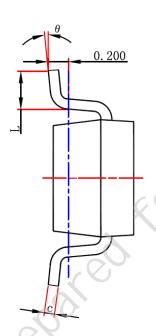

# 11. Package Information (SOT23-6)

| Cumb a l | Dimensions In Millimeters |            | Dimensions In Inches |       |

|----------|---------------------------|------------|----------------------|-------|

| Symbol   | Min.                      | Max.       | Min.                 | Max.  |

| Α        | 1.050                     | 1.250      | 0.041                | 0.049 |

| A1       | 0.000                     | 0.100      | 0.000                | 0.004 |

| A2       | 1.050                     | 1.150      | 0.041                | 0.045 |

| b- 0     | 0.300                     | 0.500      | 0.012                | 0.020 |

| C        | 0.100                     | 0.200      | 0.004                | 0.008 |

| D        | 2.820                     | 3.020      | 0.111                | 0.119 |

| E1       | 1.500                     | 1.700      | 0.059                | 0.067 |

| E        | 2.650                     | 2.950      | 0.104                | 0.116 |

| е        | 0.950                     | 0.950(BSC) |                      | (BSC) |

| e1       | 1.800                     | 2.000      | 0.071                | 0.079 |

| L        | 0.300                     | 0.600      | 0.012                | 0.024 |

| θ        | 0°                        | 8°         | 0°                   | 8°    |